CIESコンソーシアム

産学共同研究

AIハードウェア 回路技術

しなやかな情報処理におけるエラー訂正技術の研究開発

-

遠藤 哲郎 教授

遠藤 哲郎 教授

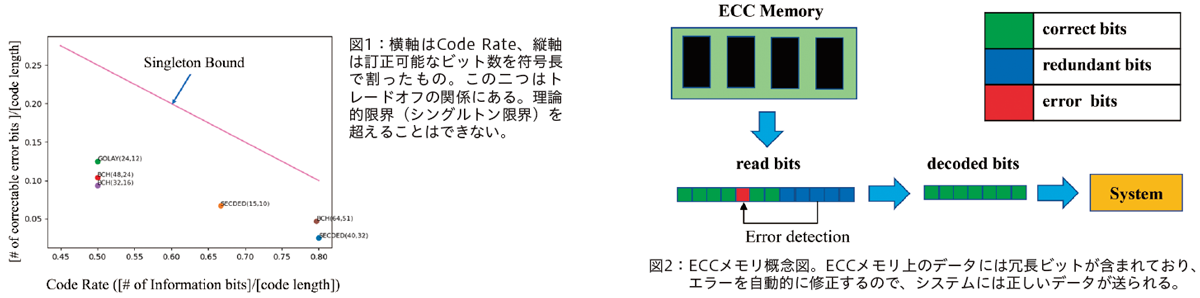

DRAMをはじめとした記憶デバイスでは宇宙線や温度条件その他の原因により記憶ビットが反転することがあり、誤った計算結果などが発生します。これらのエラーを検出し訂正する「誤り訂正符号(ECC, Error Correction Code)」の技術が発展してきました。ECC技術では、元々のデータを冗長性を持った誤り訂正符号に変換し、エラーが混入してもそれを検知し元々のデータを復元できるようにします。ただし、訂正能力を上げる=より多くのエラーを検知・訂正するには、その能力に応じた大きな冗長性が必要となります(図1)。

コンピュータにおける重要な部品である「メモリ」にも誤り訂正符号の技術が使われており、特にハードウェアとしてECC回路を実装しているメモリを「ECCメモリ」と呼びます。通常、ECCメモリでは、1bitのエラーの訂正と2bitのエラーの検出が可能な「SECDED」というECCアルゴリズムがよく使われてきました。本テーマではSECDEDに限らずSTT-MRAMにとって最適で訂正能力の高いECCアルゴリズムを試行錯誤の容易なソフトウェアベースで探求・検証しており、BCH符号、Golay符号等のECCアルゴリズムの実装・改良を行ってきました。BCH符号はある制約の下、訂正可能なビット数を選ぶことができます。一方、Golay符号は符号長や訂正可能なビット数は決まっていますが、BCH符号よりも簡易な計算でエラーを検知・訂正してデータを復元することができます。