CIES Consortium

National Projects

NEDO Project for Research and Development of Enhanced Infrastructures for Post 5G Information and Communications Systems

Feasibility study /

Research and development of microfabrication core technologies for nonvolatile MRAM at 1.5nm node and beyond

-

R&D Director (TEL)

R&D Director (TEL)

Takashi Hayakawa -

Prof.

Prof.

Shoji Ikeda

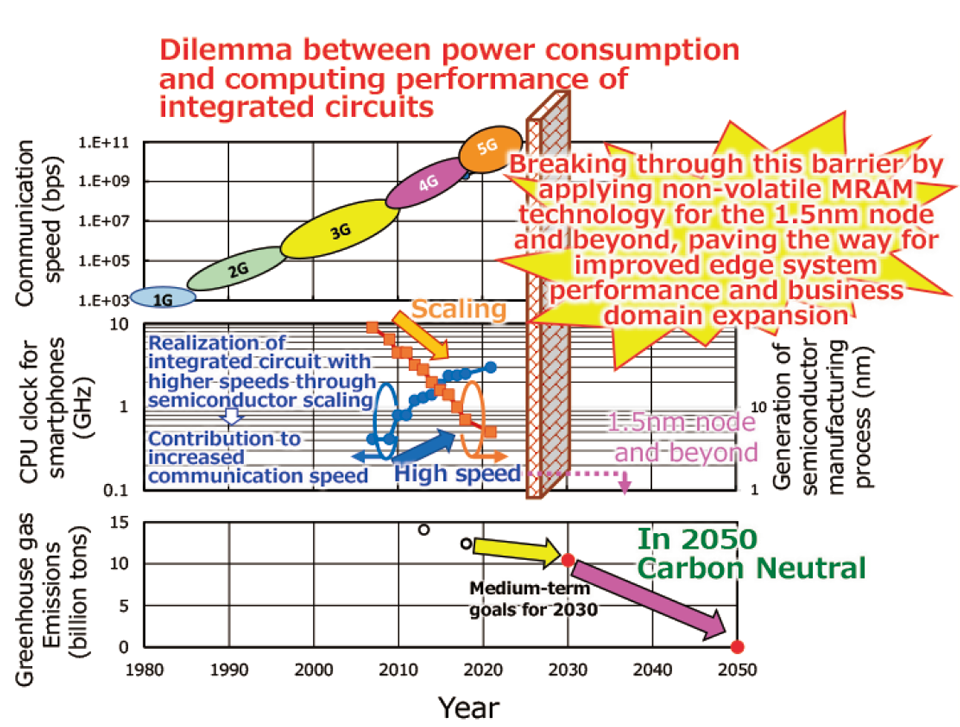

In order to achieve low latency in the post-5G era for edge-side systems such as smartphones and IoT/AI processors, high performance edge computing is necessary under the power supply limitation environment. However, the dilemma of power consumption and computing performance will continue to be an issue in the development of technologies beyond the 1.5nm node, which is an extension of conventional silicon technologies. As a result, there will be limitations in advancing the performance of edge systems and expanding their business fields.

In this theme, research and development of microfabrication technology for nonvolatile MRAM at the 1.5nm node and beyond will contribute to overcoming the dilemma between power consumption and computing performance by reducing power consumption through nonvolatility and miniaturization based on MRAM/CMOS hybrid LSI technology. This will enable the realization of edge-side systems with low power consumption and low latency for the post-5G era, and contribute to carbon neutrality as a synergistic effect of its social implementation.

Based on the following, we will develop fundamental microfabrication technologies for nonvolatile MRAM for the semiconductor process 1.5nm node and beyond;

Tokyo Electron Limited (TEL): Development of core technology for RIE etching at MTJ pitch for the 1.5nm node and beyond Tohoku University, CIES: Processes development, fabrication, and evaluation to verify the developed RIE technology